# uc3m Universidad Carlos III de Madrid

## Subsistemas de Radiofrecuencia y Antenas

## Diseño de un array de antenas en banda K

## **Alumnos:**

Eduardo Gómez González Óscar González Fresno Oier Huici Itarte

# Índice

| 1.         | Intr | oducci   | on .                    |                    |     |       | 2      |

|------------|------|----------|-------------------------|--------------------|-----|-------|--------|

| 2.         | Esp  | ecificae | iones                   |                    |     |       | 2      |

| 3.         | Met  | odolog   | ía                      |                    |     |       | 3      |

| 4.         | Dise | eño de   | la práctica             |                    |     |       | 5      |

|            | 4.1. | Red de   | alimentación activa .   |                    |     | <br>  | <br>5  |

|            |      | 4.1.1.   | Amplificador de bajo 1  | ruido              |     | <br>  | <br>5  |

|            |      |          | I. Condiciones          | de polarización .  |     | <br>  | <br>5  |

|            |      |          | II. Obtención de        | e las cargas       |     | <br>  | <br>6  |

|            |      |          | III. Optimización       | del diseño ideal   |     | <br>  | <br>11 |

|            |      | 4.1.2.   | Divisor pasivo de pote  | ncia de tres puert | cos | <br>  | <br>15 |

|            |      |          | I. Cálculo teóri        | co                 |     | <br>  | <br>15 |

|            |      |          | II. Primer diseñe       | 0                  |     | <br>  | <br>16 |

|            |      |          | III. Segundo dise       | ño                 |     | <br>  | <br>18 |

|            |      |          | IV. Tercer diseño       | )                  |     | <br>  | <br>19 |

|            | 4.2. | Layout   | de la parte activa      |                    |     | <br>  | <br>21 |

|            |      | 4.2.1.   | Circuito de polarizació | n                  |     | <br>  | <br>21 |

|            |      | 4.2.2.   | Divisor de potencia .   |                    |     |       |        |

|            | 4.3. | Elemen   | to radiante             |                    |     |       |        |

|            |      |          | Antena de parche con    |                    |     |       |        |

|            |      |          | -                       | es de campo elécti |     |       |        |

|            |      |          |                         | les                | •   | <br>~ | 32     |

|            |      |          | -                       | e radiación        |     |       |        |

|            |      | 4.3.2.   | Antena de parche con    |                    |     |       |        |

|            |      | 4.3.3.   | Array de antenas        | -                  |     |       |        |

| <b>5</b> . | Inte | gració   | l                       |                    |     |       | 39     |

|            |      | clusion  |                         |                    |     |       | 11     |

## 1. Introducción

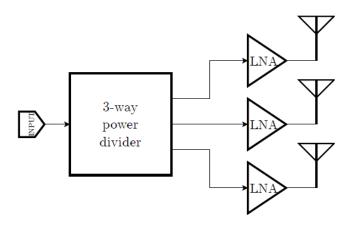

La parte práctica de esta asignatura tiene como objetivo principal el diseño inicial de la parte hardware de un radar en funcionamiento en la banda K, que abarca frecuencias de  $18-27\,\mathrm{GHz}$ . En este proceso, es esencial contar con una red de alimentación activa de tipo corporativo que alimente un conjunto de tres antenas, como se ilustra en la Figura 1.

Figura 1: Esquema general de la práctica

La elección de utilizar tres antenas se basa en la búsqueda de un diagrama direccional adecuado, con el mayor alcance posible. Esta elección también respalda la decisión de emplear una red activa en lugar de una pasiva. Dado que se pretende que el sistema sea portátil, debido a su tamaño reducido por la alta frecuencia de operación, el apuntamiento del diagrama se llevará a cabo de forma mecánica en lugar de electrónica. Para simplificar aún más el diseño, se ha optado por una alimentación que mantiene la misma fase para todos los elementos radiantes del conjunto.

El objetivo final no se limita sólo al cumplimiento de las especificaciones de la práctica, sino que también implica el desarrollo de un circuito que sea fabricable y medible con un grado razonable de éxito. Para lograr esto, se emplearán extensivamente herramientas como AWR en el diseño de la red de alimentación activa y CST en el análisis de los elementos radiantes. Posteriormente, ambas partes se unirán, prestando especial atención a la generación del circuito impreso completo.

## 2. Especificaciones

La frecuencia central del trabajo  $f_0$  depende de cada grupo de prácticas con

$$f_0 = f_c + \Delta f[\text{GHz}] \tag{1}$$

tomando  $f_c = 18 \text{ y}$

$$\Delta f = \frac{2}{3N} \sum_{i}^{N} X_i \tag{2}$$

siendo  $X_i$  la última cifra del NIA del estudiante i-ésimo.

En este caso se tiene que,

$$\Delta f = \frac{2}{3 \cdot 3} (0 + 2 + 1) = 0,66 \,\text{GHz}$$

por lo que la frecuencia central de trabajo resulta en:

$$f_0 = 18 + 0.66 \,\mathrm{GHz} = 18.66 \,\mathrm{GHz}$$

La aplicación es de banda estrecha, por lo que todos los diseños se requieren que estén centrados en la frecuencia  $f_0$  pero sin requisitos específicos de ancho de banda. Para la fabricación, se ha considerado un límite de fabricación de 100 µm para las pistas y de 50 µm para la separación entre pistas.

Por último, los requisitos finales de cada bloque construido se detallan en los Cuadros 1, 2 y 3.

| Figura de ruido      | 1,1 dB |

|----------------------|--------|

| Ganancia             | 11 dB  |

| Adaptación de salida | 20 dB  |

Cuadro 1: Amplificador de bajo ruido

| Adaptación de entrada       | 20 dB             |

|-----------------------------|-------------------|

| Adaptación de salida        | 15 dB             |

| Aislamiento entre puertos   | 15 dB             |

| Desequilibrio entre puertos | $0.5~\mathrm{dB}$ |

Cuadro 2: Divisor de potencia

| Adaptación                 | 14 dB |

|----------------------------|-------|

| Directividad (de al menos) | 7 dBi |

Cuadro 3: Elemento radiante

## 3. Metodología

Para el desarrollo de la práctica, ha sido necesario un trabajo analítico previo a cada jornada de laboratorio que sentase las bases sobre las que trabajar en cada sesión. El material empleado para esta práctica han sido fundamentalmente dos programas de *software*: AWR y CST.

El primero de ellos ha servido para el diseño del circuito activo, permitiendo calcular las cargas elegidas según los requerimientos pedidos. El amplificador elegido para la red de alimentación activa es el proporcionado por el fabricante CEL, concretamente su modelo CE3521M4 <sup>1</sup>. También se ha diseñado en este programa el divisor de potencia de tipo Wilkinson. AWR

https://www.cel.com/documents/datasheets/CE3521M4.pdf

no sólo ha permitido crear un esquemático de la red activa, sino que también ha posibilitado realizar un diseño con líneas reales y ver su correspondiente en líneas microstrip con el sustrato elegido.

Por otro lado, CST se usó para el cálculo de los elementos radiantes. Primeramente se realizó un estudio de una antena de parche con plano de masa infinito, para posteriormente considerar un diseño con plano de masa finito. Una vez realizado, se aplico ese diseño a una agrupación de dos antenas.

Finalmente, se integró el array de antenas creado en CST en la red de alimentación activa diseñada en AWR y se analizó el comportamiento del diseño en su conjunto.

## 4. Diseño de la práctica

En esta sección se abordará por separado cada una de las partes en las que se ha dividido la práctica, dando una visión más detallada de los retos de cada una.

#### 4.1. Red de alimentación activa

La red de alimentación activa consiste en un amplificador de bajo ruido que se situará en la salida del divisor de potencia en tres ramas, como se indica en la Figura 1.

#### 4.1.1. Amplificador de bajo ruido

Para el diseño de la parte activa del circuito se ha tomado como elemento amplificador el modelo CE3521M4 de CEL, que está especialmente diseñado para minimizar el ruido a altas frecuencias.

Atendiendo a su hoja de características, podemos obtener la figura de ruido esperada para la frecuencia de trabajo deseada. En este caso tenemos que, para unas condiciones de polarización dadas tales que  $V_{DS}=2\,\mathrm{V}, I_D=10\,\mathrm{mA}$  y  $f=20\,\mathrm{GHz}$ , la figura de ruido típica es:

$$NF = 0.7 \, \mathrm{dB}$$

#### I. Condiciones de polarización

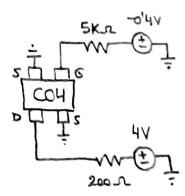

Sabiendo entonces las condiciones de polarización, se puede determinar el circuito de polarización, detallando fuentes de corriente y elementos resistivos que cumplan con las condiciones indicadas por el fabricante.

En primer lugar, de las gráficas proporcionadas en el datasheet del fabricante se obtiene que para unas condiciones de  $V_{DS} = 2 \text{ V}$  e  $I_D = 10 \text{ mA}$ , la tensión  $V_{GS} = -0.4 \text{ V}$ . Con esto, se procede a obtener el valor de la fuente de tensión y la resistencia que se conectarán al drenador del amplificador:

$$\frac{V_{source} - V_{DS}}{I_D} = R_D \tag{3}$$

Para un valor de  $V_{source} = 4 \, \text{V}$ , se obtiene una  $R_D = 200 \, \Omega$ . Por otra parte, la fuente de tensión que se coloca en la puerta tendrá un valor de  $V_{GS} = -0.4 \, \text{V}$ , y se escoge un valor alto para dicha resistencia, como  $R_G = 5000 \, \Omega$ , para que circule poca corriente. El circuito resultante se muestra en la Figura 2.

Figura 2: Circuito de polarización con circuito integrado

Por último, es necesario que el circuito de polarización quede completamente aislado del circuito de radiofrecuencia, y viceversa, por lo que se deben añadir elementos capacitivos e inductivos que hagan esta función. Los condensadores y bobinas que se muestran en el circuito de la Figura 3 realizan esta función, así como la de aislar la etapa de RF de otras posibles existentes.

Figura 3: Circuito de polarización con elementos de aislamiento

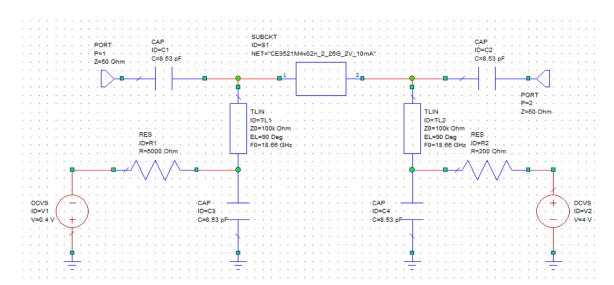

Una vez estudiado el circuito de polarización, el siguiente paso ha sido la obtención de las cargas. Para ello, lo primero ha sido sacar los parámetros S del amplificador y ver primeramente cómo se comporta en la banda K de frecuencias.

#### II. Obtención de las cargas

Dada la hoja de características del fabricante, se puede observar que para una frecuencia de  $18,66\,\mathrm{GHz}$ , los parámetros S correspondientes al transistor son los siguientes:

$$S = \begin{bmatrix} 0.6353353_{96,277^{\circ}} & 0.1064028_{-26,231^{\circ}} \\ 3.0161452_{-43,164^{\circ}} & 0.2097688_{118,066^{\circ}} \end{bmatrix}$$

(4)

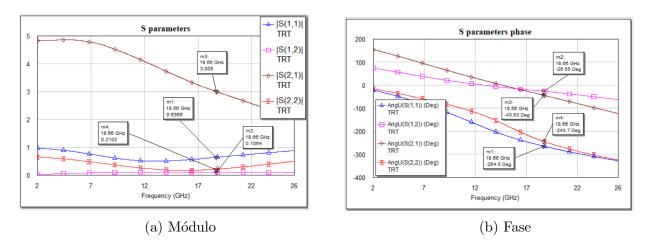

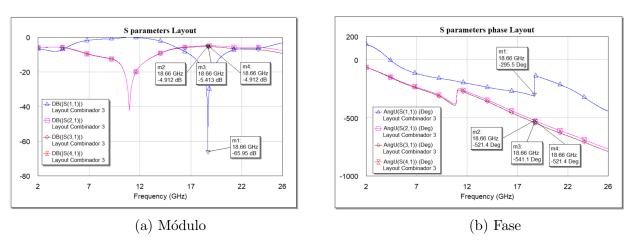

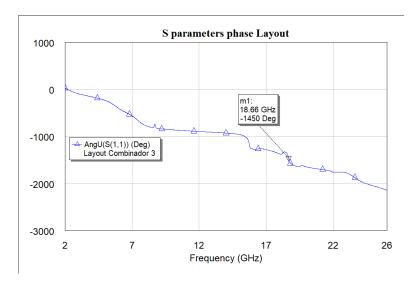

Una vez obtenida la matriz de *scattering*, el siguiente paso ha sido ver la respuesta en frecuencia del transistor para un rango de 2 a 26 GHz. Los resultados obtenidos se muestran en la Figura 4, en la que se distingue entre módulo (4a) y fase (4b). Nótese que se han añadido marcadores que indican los valores exactos en módulo y fase para la frecuencia de trabajo.

Figura 4: Parámetros S

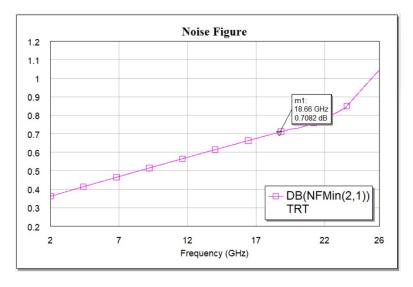

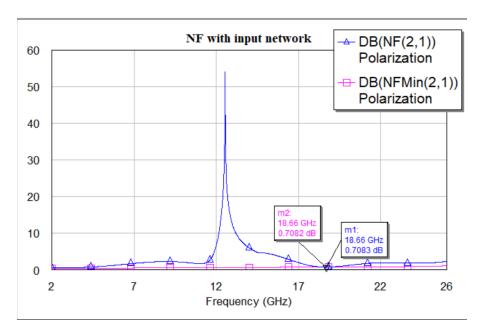

Otro parámetro de interés es el de la figura de ruido (Figura 5), que da información sobre la degradación de la relación señal/ruido provocada por el dispositivo, cuando el ruido en su entrada es el que corresponde a la temperatura estándar  $T_0$ .

Figura 5: Figura de ruido

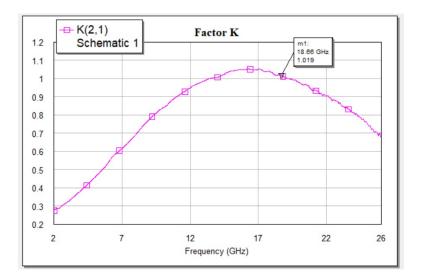

Siguiendo con el estudio de las características del transistor, se presenta a continuación uno de los criterios más comunes en el diseño de amplificadores, como es el de la estabilidad. Para evaluarla, la figura de mérito que se puede emplear es la del factor de Rollet,

$$K = \frac{1 + |\Delta|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{12}S_{21}|} \tag{5}$$

donde  $\Delta$  es el determinante de la matriz de *scattering*. Es deseable que el transistor trabaje en la zona estable, pero no simpre se puede satisfacer esta condición. Se dice que un amplificador es incondicionalmente estable cuando se cumplen las siguientes condiciones.

$$\begin{cases}

K > 1 \\

|\Delta| < 1

\end{cases}

\tag{6}$$

Si se da esta situación, se puede afirmar que el amplificador es estable para cualquier carga conectada. Por tanto, interesa comprobar si esta es la situación para la matriz S correspondiente a  $18,66\,\mathrm{GHz}$ .

Figura 6: Factor de Rollet

En la Figura 6 se muestran distintos valores de K para un determinado rango de frecuencias. Se puede observar que el valor de K para la frecuencia de trabajo es igual a 1.019. Esto es condición necesaria pero no suficiente, ya que aún queda evaluar el determinante de la matriz de scattering. En este caso, se tiene que  $|\Delta|=0.1862$ , por lo que podemos afirmar que el transistor es incondicionalmente estable.

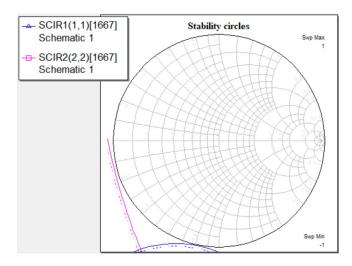

Además de la obtención de la figura de mérito, se puede llegar a la misma conclusión estudiando las circunferencias de estabilidad. En la Figura 7 se puede apreciar cómo, tanto la circunferencia de estabilidad a la entrada como la circunferencia de estabilidad a la salida se encuentran fuera de la Carta de Smith sin llegar a cortarse en ningún momento, lo cuál implica que el transistor es incondicionalmente estable. Pese a esta condición, sí es notable cómo estas circunferencias están muy próximas al borde de la carta, llegando a ser casi tangentes. Este hecho es comparable con el valor muy próximo a la unidad del Factor de Rollet para la frecuencia de trabajo. Se tendrá en cuenta esta condición al realizar el diseño.

Figura 7: Circunferencias de estabilidad

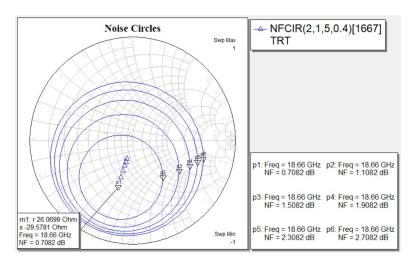

Otro factor interesante de estudio es el de las circunferencias de ruido. Con ellas se pueden obtener las impedancias de entrada que dan una figura de ruido determinada. Las circunferencias representan valores de ruido constante, están alineadas en sus centros y convergen en un punto, que es el de mínimo ruido. En la Figura 8 se muestran varias circunferencias distanciadas 0.5 dB entre sí. Se puede observar cómo el punto de convergencia  $(F_{opt})$  coincide con el valor de la Figura 5.

Figura 8: Circunferencias de ruido

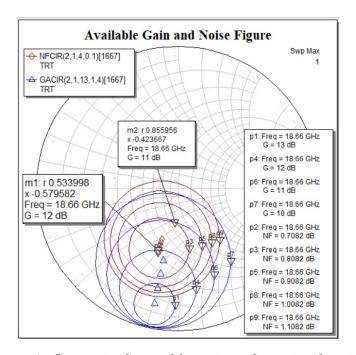

Una vez estudiadas las características del amplificador, ya es posible abordar el problema de la elección de las cargas. Tomando como punto inicial las condiciones de entrada, se tiene que se debe cumplir con que la figura de ruido no sea mayor de 1,1 dB y que la ganancia del sistema sea igual a 11 dB. Con esto presente, es fácil obtener la carga a la entrada si se dibujan las circunferencias de ruido y la circunferencia de ganancia disponible a 11 dB, como se muestra en la Figura 9.

Figura 9: Ganancia disponible y circunferencias de ruido

Se puede observar cómo hay múltiples combinaciones para elegir el valor de la impedancia de entrada. De todas ellas, podemos quedarnos con las dos más interesantes, que serían las indicadas en los marcadores.

La primera opción posible sería la elección de una carga que aporta el mínimo ruido de entrada (m1) y resulta en una ganancia 1 dB superior a la propuesta. La segunda opción es tomar un valor de ganancia de 11 dB y ver su corte con la circunferencia de ruido (m2), que resulta ser mejor que el requerido pero no tan bueno como el óptimo. Ambas combinaciones cumplen con los requisitos pedidos, así que se podría elegir cualquiera. Sin embargo, como en la segunda opción la carga resultante está más alejada de la zona de estabilidad, es preferible elegirla como impedancia de entrada. Por tanto, se tiene que:

$$\begin{cases} F = 0,8082 \, \text{dB} \\ G_a = 11 \, \text{dB} \\ \widetilde{z}_s = 0,855956 - j0,423667 \,\Omega \end{cases}$$

(7)

Una vez obtenida la carga a la entrada, se puede obtener fácilmente la carga a la salida gracias a la siguiente ecuación:

$$\Gamma_{out} = S_{22} + \frac{S_{12}S_{21}\Gamma_{S}}{1 - S_{11}\Gamma_{S}} \tag{8}$$

siendo  $\Gamma_s = -0.02424 - j0.2338 \Omega$ . Adaptando la salida, se puede obtener fácilmente la impedancia de salida como  $\Gamma_L = \Gamma_{out}^*$ , lo equivale a decir que la salida está perfectamente adaptada  $(M_2 = 1)$ . Por tanto, a la salida se tiene que:

$$\Gamma_{out} = 0,2458_{138,61^{\circ}} \Rightarrow \Gamma_L = 0,2458_{-138,61^{\circ}}$$

(9)

resultando en una impedancia de salida de  $\widetilde{z}_L = 0.657343 - j0.227415\,\Omega$ .

Finalmente, se obtiene:

$$\begin{cases} F = 0.8082 \, \text{dB} \\ G_t = G_a M_2 = 11 \, \text{dB} \\ \widetilde{z}_S = 0.855956 - j0.423667 \, \Omega \\ \widetilde{z}_L = 0.657343 - j0.227415 \, \Omega \end{cases}$$

(10)

#### III. Optimización del diseño ideal

Hasta ahora se han presentado todos los resultados para un circuito en el que sólo se disponía del amplificador, sin ningún añadido. Con motivo de incorporar el amplificador a un circuito, es necesario introducir un circuito de polarización, que además de fijar el punto de polarización, cumpla lo siguiente:

- La señal RF no debe introducirse en el circuito DC.

- El circuito RF no debe verse afectado por el circuito DC.

- Aisle las etapas de RF.

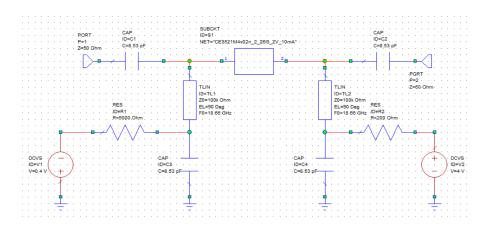

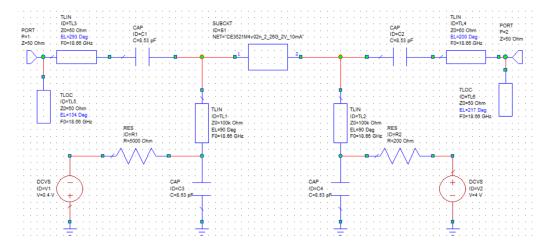

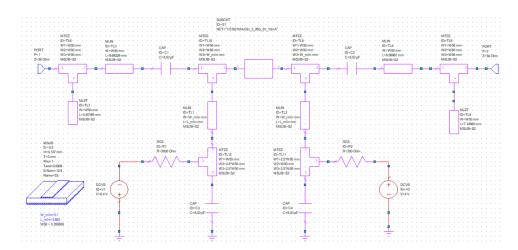

El estudio del circuito de polarización abordado anteriormente en el Apartado I se ha traslado al programa de simulación. La Figura 10 muestra la implementación del circuito de la Figura 2 en el programa AWR, donde se han sustituido las bobinas por trozos de línea de alta impedancia.

Figura 10: Circuito de polarización

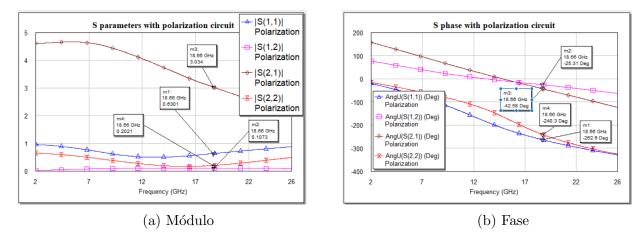

En la Figura 11 se muestran los valores en módulo (11a) y fase (11b) de los parámetros S con el circuito de polarización añadido. Se puede apreciar una ligera diferencia en algunos de los parámetros, casi despreciable, que puede ser debida a que la polarización afecta directamente al punto de operación del transistor.

Figura 11: Parámetros S

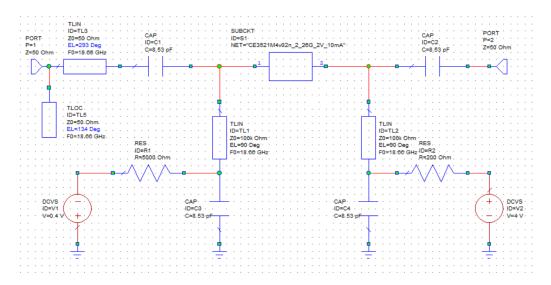

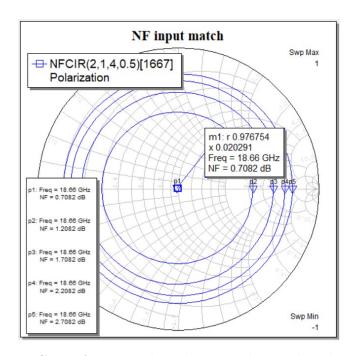

A continuación, se pretende observar el comportamiento del amplificador al añadir un circuito de adaptación a la entrada, de modo que se introduzca el mínimo ruido. Para ello, se añade un doble stub a su entrada. Pese a los cálculos teóricos realizados anteriormente, sabiendo que el amplificador asignado es incondicionalmente estable a la frecuencia de trabajo, se ha decidido ajustar las longitudes eléctricas de los stubs serie y paralelo con la herramienta Tuner de AWR para obtener el mínimo ruido a la entrada. Con ello, se obtienen una longitud eléctrica de 293° para el stub serie y de 134° para el paralelo:

Figura 12: Circuito con adaptación a la entrada

Figura 13: Figura de ruido a la entrada con adaptación

Los círculos de ruido a la frecuencia de trabajo asginada son los siguientes:

Figura 14: Circunferencias de ruido con adaptación a la entrada

Se observa que la figura de ruido mínima no ha cambiado ya que es una característica intrínseca, sin embargo los círculos de ruido se encuentran en posiciones diferentes.

A continuación, se introduce un circuito de adaptación a la salida para obtener los  $20\,\mathrm{dB}$  de adaptación requeridos. De la misma forma que para la red de entrada, se utiliza un doble stub cuyas longitudes eléctricas se ajustan mediante la herramienta Tuner de AWR para obtener los parámetros de diseño deseados. Las longitudes eléctricas obtenidas son  $200^\circ$  para el stub serie y  $217^\circ$  para el paralelo.

Figura 15: Circuito con adaptación a la entrada y a la salida

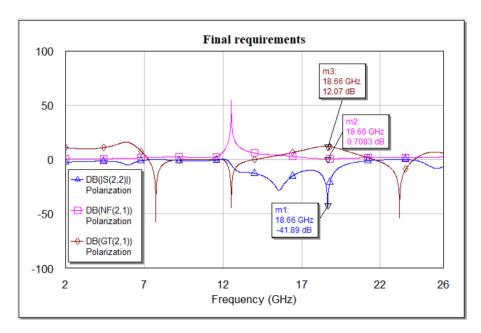

Figura 16: Valores finales de los parámetros de diseño

En la figura anterior se observa, en primer lugar, que la figura de ruido no cambia, ya que esta solo depende de la red de adaptación a la entrada. Además, los parámetros de diseño finales obtenidos cumplen los requisitos pedidos.

$$\begin{cases} G_T = 12,07 \, dB > 11 \, dB \\ S_{22} = -41,89 \, dB < -20 \, dB \\ NF = 0,7083 \, dB < 1,1 \, dB \end{cases}$$

(11)

#### 4.1.2. Divisor pasivo de potencia de tres puertos

Se desea que la división de potencia se realice en partes iguales en tres ramas, obteniendo la misma fase relativa en las tres salidas. Por lo tanto, se busca la siguiente matriz de *scattering*:

$$[S] = \begin{bmatrix} 0 & \tau e^{j\theta} & \tau e^{j\theta} & \tau e^{j\theta} \\ \tau e^{j\theta} & 0 & 0 & 0 \\ \tau e^{j\theta} & 0 & 0 & 0 \\ \tau e^{j\theta} & 0 & 0 & 0 \end{bmatrix}$$

(12)

donde  $\tau$  y  $\phi$  son respectivamente el módulo y la fase del parámetro de transmisión.

#### I. Cálculo teórico

En primer lugar, como se quiere implementar un divisor de potencia en tres partes iguales, en un caso ideal sin pérdidas 1/3 de la potencia de entrada saldrá por cada uno de los puertos de salida, por lo que el máximo valor del módulo del parámetro de transmisión será:

$$\tau = \frac{1}{\sqrt{3}} \Rightarrow -4,77 \, \mathrm{dB} \tag{13}$$

Por otra parte, a la vista de la matriz de scattering del circuito, este será recíproco ya que se cumple la relación  $S_{ij} = S_{ji}$  entre sus elementos. Además, para que el circuito sea sin pérdidas, su matriz de scattering debe cumplir lo siguiente  $[S]^t[S]^* = [I]$ , siendo [I] la matriz identidad.

$$\begin{bmatrix} 0 & \tau e^{j\theta} & \tau e^{j\theta} & \tau e^{j\theta} & \tau e^{j\theta} \\ \tau e^{j\theta} & 0 & 0 & 0 \\ \tau e^{j\theta} & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} 0 & \tau e^{-j\theta} & \tau e^{-j\theta} & \tau e^{-j\theta} \\ \tau e^{-j\theta} & 0 & 0 & 0 \\ \tau e^{-j\theta} & 0 & 0 & 0 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1/3 & 1/3 & 1/3 \\ 0 & 1/3 & 1/3 & 1/3 \\ 0 & 1/3 & 1/3 & 1/3 \end{bmatrix}$$

(14)

A la vista del cálculo anterior, se puede afirmar que el circuito no será sin pérdidas.

Para la realización de la práctica, se ha optado por diseñar un divisor de potencia en tres ramas basado en divisores de potencia de tipo Wilkinson simétricos o asimétricos, a pesar de existir otras posibilidades de diseño. La matriz [s] de un divisor Wilkinson simétrico es de la forma:

$$S = \frac{-j}{\sqrt{2}} \begin{bmatrix} 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 0 \end{bmatrix} \tag{15}$$

y, en cambio, la de uno asimétrico definiendo la relación de potencia entre los puertos 2 y 3 como  $K^2 = P_3/P_2$ :

$$S = -j \begin{bmatrix} 0 & \frac{1}{\sqrt{1+K^2}} & K \frac{1}{\sqrt{1+K^2}} \\ \frac{1}{\sqrt{1+K^2}} & 0 & 0 \\ K \frac{1}{\sqrt{1+K^2}} & 0 & 0 \end{bmatrix}$$

(16)

Particularizando la anterior para una relación 2:1 entre los puertos de salida, es decir  $K^2=2$  se obtiene:

$$S = -j \begin{bmatrix} 0 & 1/\sqrt{3} & \sqrt{2/3} \\ 1/\sqrt{3} & 0 & 0 \\ \sqrt{2/3} & 0 & 0 \end{bmatrix}$$

(17)

Finalmente, se obtiene la respuesta del divisor completo de potencia en tres puertos de salida con igual fase, resultado de combinar Wilkinson simétricos y asimétricos:

$$S = \frac{1}{\sqrt{3}} \begin{bmatrix} 0 & 1 & 1 & 1\\ 1 & 0 & 0 & 0\\ 1 & 0 & 0 & 0\\ 1 & 0 & 0 & 0 \end{bmatrix}$$

(18)

#### II. Primer diseño

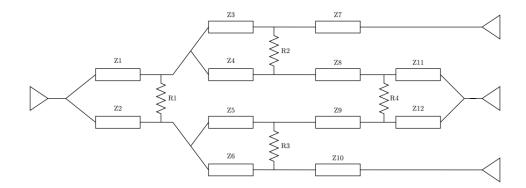

Una vez realizado el desarrollo teórico, se puede proceder a su implementación en el software de simulación. Primeramente, se plantea el diseño mostrado en la Figura 17, donde los rectángulos son tramos de línea de longitud eléctrica  $90^{\circ}$  y los triángulos son los puertos de entrada y de salida.

Figura 17: Primer diseño posible de divisor de potencia

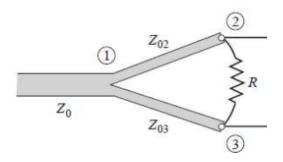

A continuación, se obtienen los valores de impedancia para cada uno de los tramos de línea y las resistencias tanto para los Wilkinson simétricos como asimétricos. Utilizando como referencia la siguiente nomenclatura para un divisor Wilkinson:

Figura 18: Divisor Wilkinson

en el caso simétrico, las ecuaciones de diseño son:

$$Z_{02} = Z_{03} = Z_0\sqrt{2}, \quad R = 2Z_0$$

(19)

y en el caso no simétrico:

$$Z_{03} = Z_0 \sqrt{\frac{1+K^2}{k^3}}, \quad Z_{02} = k^2 Z_{03}, \quad R = Z_0 (k+\frac{1}{k})$$

(20)

Con ello, los valores obtenidos en ohmnios se presentan en la siguiente tabla.

| <b>Z</b> 1    | ${f Z2}$    | <b>Z</b> 3    | ${f Z4}$      |

|---------------|-------------|---------------|---------------|

| 70.71         | 70.71       | 51.49         | 102.99        |

| $\mathbf{Z}5$ | ${f Z}6$    | $\mathbf{Z}7$ | $\mathbf{Z}8$ |

| 102.99        | 51.49       | 45.05         | 59.46         |

| <b>Z</b> 9    | <b>Z</b> 10 | <b>Z</b> 11   | <b>Z</b> 12   |

| 59.46         | 42.05       | 70.71         | 70.71         |

| R1            | R2          | R3            | R4            |

| 100           | 106.07      | 106.07        | 100           |

Cuadro 4: Valores de impedancias y resistencias (en  $\Omega$ ) del primer diseño

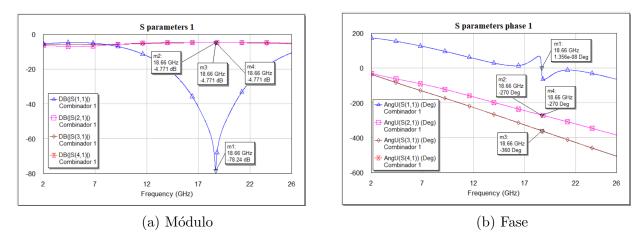

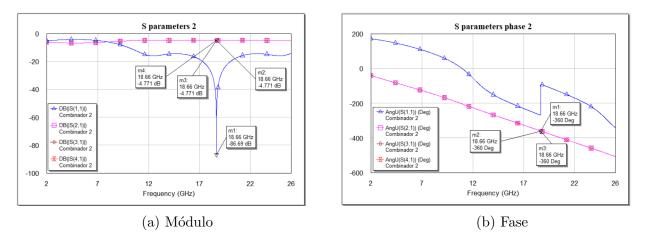

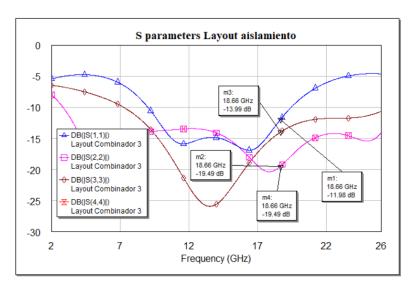

El módulo y la fase de los parámetros S más relevantes se muestran en la siguiente figura:

Figura 19: Parámetros S para el primer diseño

Se observa que el comportamiento en módulo de los parámetros obtenidos es el deseado, ya que se obtiene una adaptación a la entrada de  $-78,24\,\mathrm{dB}$  y en cada una de las salidas se obtiene una relación respecto a la entrada de  $-4,771\,\mathrm{dB}$ , es decir, un tercio de la potencia de entrada se encuentra en cada una de las salidas. Por otra parte, con respecto a la fase, se aprecia que el comportamiento no es el deseado ya que no se obtiene la misma en las tres salidas.

#### III. Segundo diseño

A continuación, se trata de mejorar la implementación anterior utilizando la configuración de la Figura 20. En este diseño el objetivo es corregir el desfase presente en el anterior entre las salidas, para lo que se eliminan los adaptadores  $\lambda/4$  ubicados en la conexión con el Wilkinson simétrico invertido que actúa como combinador.

Figura 20: Segundo diseño posible de divisor de potencia

En este caso, para conseguir adaptación a la entrada del circuito se deben multiplicar las impedancias y resistencias de ambos divisores asimétricos por k, por lo que las líneas Z3 y Z4 se utilizarán como adaptadores. Los valores introducidos en las impedancias y resistencias, en ohmios, son los siguientes:

| <b>Z</b> 1 | $\mathbf{Z}2$ | <b>Z</b> 3  | ${f Z4}$    |

|------------|---------------|-------------|-------------|

| 70.71      | 70.71         | 42.04       | 42.04       |

| <b>Z</b> 5 | <b>Z</b> 6    | <b>Z</b> 7  | <b>Z</b> 8  |

| 36.41      | 72.82         | 72.82       | 36.41       |

| <b>Z</b> 9 | <b>Z</b> 10   | <b>Z</b> 11 | <b>Z</b> 12 |

| 35.36      | 35.36         | 70.71       | 70.71       |

| R1         | R2            | R3          | R4          |

| 100        | 75            | 75          | 100         |

Cuadro 5: Valores de impedancias y resistencias (en  $\Omega$ ) del segundo diseño

Los parámetros S obtenidos son:

Figura 21: Parámetros S para el segundo diseño

De la figura anterior se deduce que la red funciona como se desea, ya que se mantiene la adaptación a la entrada y la división de potencia igual en cada salida, además de obtenerse la misma fase en los tres puertos de salida.

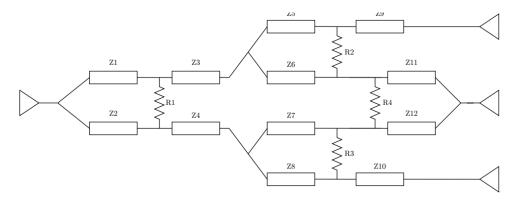

#### IV. Tercer diseño

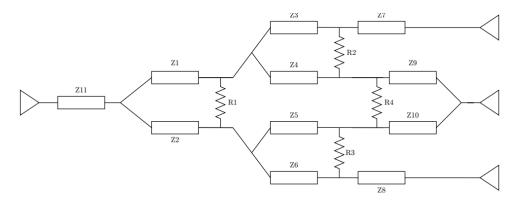

Como última opción, se decide implementar el diseño de la Figura 22. En esta, se eliminan los dos adaptadores situados a la salida del primer divisor Wilkinson simétrico y se coloca solamente un adaptador a la entrada del circuito.

Figura 22: Tercer diseño posible de divisor de potencia

Para que esta configuración funcione correctamente, se deben multiplicar tanto las impedancias como la resistencia del primer Wilkinson simétrico por k y calcular el valor del adaptador  $\lambda/4$  situado en la entrada (Z11). Los valores escogidos, en ohmios, son:

| <b>Z</b> 1    | ${f Z2}$       | <b>Z</b> 3  | <b>Z</b> 4 |

|---------------|----------------|-------------|------------|

| 50            | 50             | 36.41       | 72.82      |

| $\mathbf{Z}5$ | ${f Z}6$       | <b>Z</b> 7  | <b>Z</b> 8 |

| 72.82         | 36.41          | 35.36       | 35.36      |

| <b>Z</b> 9    | $\mathbf{Z}10$ | <b>Z</b> 11 |            |

| 70.71         | 70.71          | 42.04       |            |

| R1            | R2             | R3          | R4         |

| 100           | 75             | 75          | 100        |

Cuadro 6: Valores de impedancias y resistencias (en  $\Omega$ ) del tercer diseño

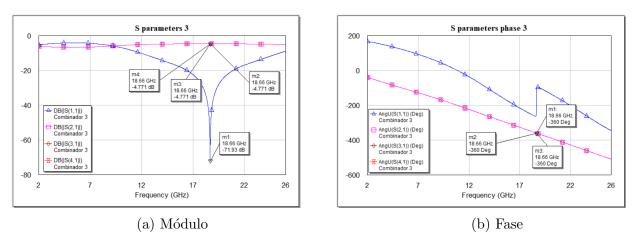

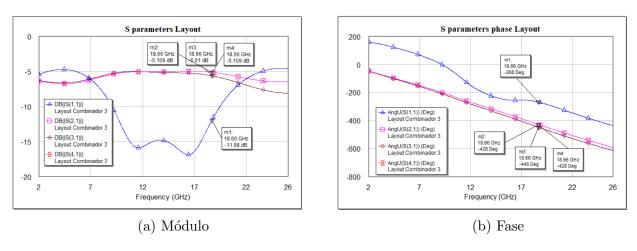

A continuación, se presentan los parámetros S obtenidos:

Figura 23: Parámetros S para el tercer diseño

Se observa que los resultados obtenidos en este caso son similares a los del diseño número 2: se obtiene adaptación a la entrada, división correcta de potencia en los puertos de salida y la misma fase en estos. Pese a tener similares prestaciones, este diseño se podría considerar mejor que el segundo en el sentido de que se utilizan menos líneas de longitud eléctrica 90º, en concreto once en lugar de doce.

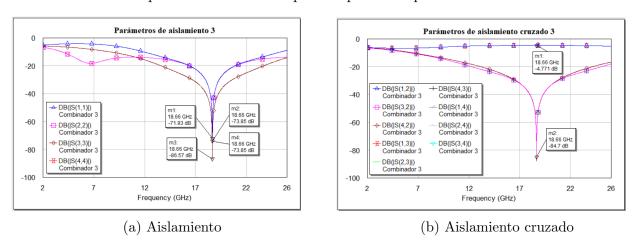

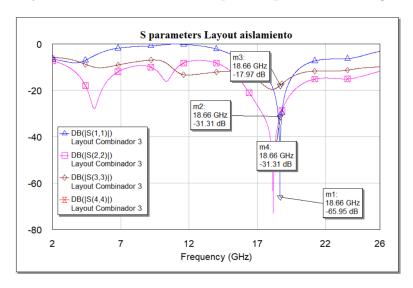

Finalmente, se simulan conjuntamente todos los parámetros de aislamiento y de aislamiento cruzado del circuito para terminar de comprobar que el comportamiento obtenido es el deseado.

Figura 24: Aislamiento y aislamiento cruzado para el tercer diseño

En la Figura 24 (a) se aprecia que todos los puertos están correctamente aislados. Además, en la Figura 24 (b) se puede observar en los parámetros S(1,2), S(1,3) y S(1,4) que el diseño puede funcionar igualmente como combinador, por lo que el sistema en conjunto se puede utilizar también como receptor. En cuanto al resto de parámetros de aislamiento cruzado, sus valores son lo suficientemente bajos como para afirmar que se cumplen las especificaciones deseadas.

### 4.2. Layout de la parte activa

Una vez realizado todo el diseño de la red activa de alimentación, se procederá a usar elementos reales para poder fabricarlo. Para ello, se elegirá uno de los sustratos presentes en la Tabla 7 sobre el que imprimir el circuito.

| Sustrato       | $\varepsilon_r$ | Tan $\delta$ (@10 GHz) | Altura $(\mu m)$ |

|----------------|-----------------|------------------------|------------------|

| RT Duroid 5880 | 2.2             | 0.0009                 | 127              |

| RO30003        | 3               | 0.001                  | 500              |

| RO30010        | 11.2            | 0.0022                 | 250              |

Cuadro 7: Propiedades de Sustratos

Teniendo en cuenta que:

- La altura del sustrato afecta la impedancia de las líneas de transmisión y puede influir en el rendimiento del amplificador.

- Una constante dieléctrica más baja tiende a proporcionar una mejor velocidad de propagación y menor pérdida de señal.

- Un factor de disipación más bajo es beneficioso para reducir las pérdidas de señal en frecuencias más altas.

La mejor opción a elegir es la del sustrato RT Duroid 5880 por presentar los mejores valores.

### 4.2.1. Circuito de polarización

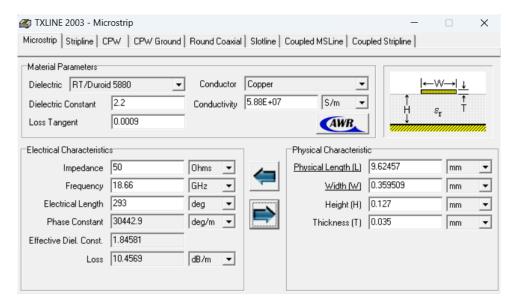

Una vez hecha esta elección, el siguiente paso es implementarlo en el circuito. Para ello, se sustituirán los tramos de línea TLIN por tramos reales MLIN y los tramos TLOC por por su correspondiente real MLEF. Para determinar el valor de su largo y ancho se hará uso de las herramientas TXLine y Tuner. La primera de ellas permite ajustar el ancho y largo de la línea mediante su valor de impedancia y su longitud eléctrica, mientras que la segunda consiste en combinar varios parámetros ajustando su valor hasta cumplir con las especificaciones.

Primeramente, para calcular los tramos de línea reales de las redes de adaptación, se ha realizado la siguiente configuración por cada tramo.

Figura 25: Cálculo del ancho y largo del stub en serie usando TXLine

Dado que las redes de adaptación están siempre conectadas a impedancias de  $50\,\Omega$ , el valor W será igual para todas,  $0.359509\,\mathrm{mm}$ . El valor que sí cambiará es de longitud de las líneas, que está relacionado con la longitud eléctrica de la línea. Con la ayuda de TXLine se obtienen los resultados de la Tabla 8.

|         | Serie   | Paralelo |

|---------|---------|----------|

| Entrada | 9.69329 | 4.40168  |

| Salida  | 6.56967 | 7.12809  |

Cuadro 8: Valores de L (mm) para las líneas reales de la red de adaptación

Una vez calculadas las longitudes y anchuras de líneas de la red de adaptación, el siguiente paso es modelar las discontinuidades. El elemento a usar para los tramos de líneas discontinuas es el llamado MTEE. Se trata de un tramo de línea en forma de T sobre el que se deben ajustar los anchos a cada extremo, haciendo que coincidan con el ancho del elemento al que está conectado.

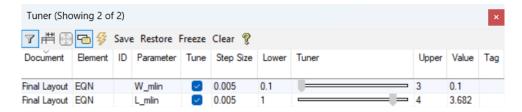

Figura 26: Uso de la herramienta *Tuner*

A continuación, se hallaron los valores de ancho (W\_mlin) y largo (L\_mlin) de las líneas que impiden que la señal RF se introduzca en el circuito DC. Tras la prueba de varias combinaciones posibles utilizando el *Tuner*, se llegó a la conclusión de que los valores que mejor se ajustan a las características deseadas son los mostrados en la Tabla 9.

| W_mlin (mm) | L_mlin (mm) |  |

|-------------|-------------|--|

| 0.1         | 3.682       |  |

Cuadro 9: Valores de W\_mlin y L\_mlin para las líneas

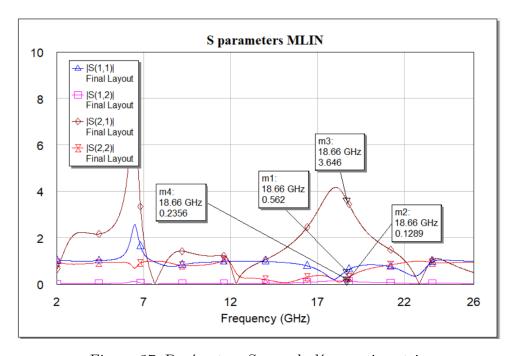

Estos valores dieron como resultado los parámetros S mostrados en la Figura 27, que distan ligeramente de los obtenidos con las líneas *TLIN*.

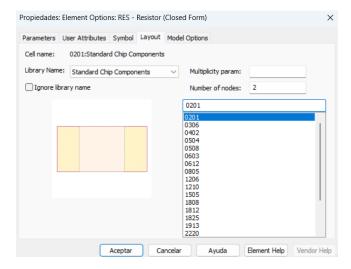

Figura 27: Parámetros S usando líneas microstrip

Tras modelar todas las líneas con las que se consigue la respuesta deseada, se introdujeron los encapsulados para conseguir un layout realizable. Para introducir el encapsulado en los elementos concentrados es necesario importar la librería de ejemplo *Standard Chip Components*. Esta librería contiene diversos modelos de encapsulados que se pueden implementar en el circuito. Uno de ellos es el 0201, que es el que se especifica en el enunciado de la práctica. Una vez importada, basta con indicar en cada resistencia y condensador que se use este modelo a la hora de realizar el layout.

Figura 28: Ejemplo de implementación del encapsulado

Por último, una vez modelados los tramos de línea, las discontinuidades y los elementos concentrados, restaría crear el modelo del layout para el transistor, las tomas de tierra y las fuentes de tensión. El fabricante del TRT recomienda usar el modelo mostrado en la Figura 29  $^{2}$

Figura 29: Modelado del transistor sugerido por el fabricante

Para el modelado de la toma de tierra y las tomas de tensión se han usado los propuestos por la profesora de la práctica. Finalmente, los modelos creados tendrían el siguiente aspecto:

<sup>&</sup>lt;sup>2</sup>https://www.cel.com/documents/K2\_K3\_M4\_layouts.pdf

La Figura 30a muestra el modelo de layout del transistor según las especificaciones del fabricante. Los pines se han realizado con la capa Air Bridge, mientras que para el encapsulado se ha empleado la capa Via. Nótese cómo, a pesar de haber 4 pines, únicamente se han conectado 2 puertos. Esta es una de las opciones posibles para realizar este modelo y se ha empleado por resultar más sencilla. Otra configuración podría haber sido añadir los dos puertos restantes y conectarlos a tierra.

El modelado de los puertos de tierra y las tomas de tensión se muestran en las Figuras 30b y 30c. Los rectángulos amarillos pertenecen a la capa Air Bridge, mientras que para la circunferencia se usa la capa Via. Se añade únicamente un puerto a masa y dos a VCC.

Figura 31: Resultado final del circuito de polarización

Finalmente, tras todos las configuraciones realizadas, el circuito resultante es el de la Figura 31. Con este diseño, el layout obtenido es el mostrado en la Figura 32.

Figura 32: Layout del circuito de polarización

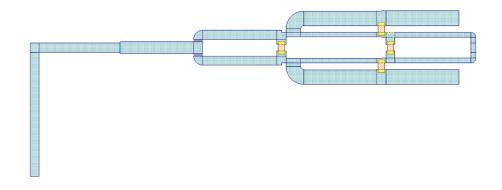

#### 4.2.2. Divisor de potencia

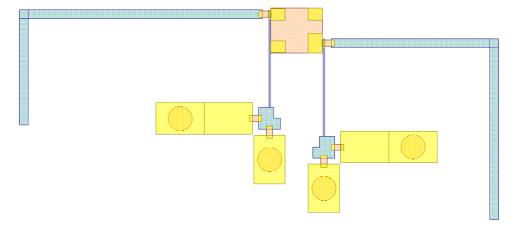

Una vez obtenido el layout del circuito de polarización, se continuó con el modelado del divisor de potencia. El trabajo fue muy similar al anterior, sustituyendo los tramos de línea TLIN por tramos MLIN, añadiendo elementos MTEE en las discontinuidades e introduciendo los encapsulados 0201 en las resistencias. Adicionalmente, fue necesario añadir trozos de

línea nuevos para encuadrar bien los elementos concentrados, así como trozos curvos de línea (MCURVE) para modelar algunas de las discontinuidades. Con todo esto, el circuito resultante es el mostrado en la Figura 33.

Figura 33: Circuito divisor de potencia con líneas reales y encapsulados

El layout obtenido se muestra en la Figura 34. En un primer instante, podría parecer que el diseño se asimila a lo esperado y por tanto darlo como válido. Sin embargo, es necesario volver a comprobar los requisitos que se piden para poder afirmar que el diseño es correcto.

Figura 34: Layout del divisor de potencia

Como ya se comentó en el Apartado 2, el divisor de potencia debe cumplir con una adaptación de 20/15 dB a su entrada y salida respectivamente. La Figura 35 muestra estas características del diseño. Se puede apreciar cómo únicamente los puertos 2 y 4 cumplen con los requisitos, mientras que el puerto de entrada está lejos de los 20 dB. El puerto 3 está cerca de cumplir con los 15 dB de aislamiento, pero se queda ligeramente por debajo.

Figura 35: Aislamiento

Otra parte fundamental del comportamiento del divisor es que reparta equitativamente la potencia de entrada a su salida, consiguiendo que por cada puerto salga un tercio de esta potencia. La Figura 36 muestra los valores de los parámetros S que determinan el valor de potencia a la salida

Figura 36: Potencia a la salida

Como se pude observar en la gráfica superior, los coeficiente de reflexión a la salida tienen un valor que ronda entre los -5,61 y -5,109 dB. Este valor indica que la potencia a la salida no exactamente un tercio (-4,77 dB) de la de entrada, sino un valor inferior, aunque sin llegar a ser su cuarta parte (-6,02 dB). Se observa además un desequilibro entre el puerto 3 y los puertos 2 y 4, habiendo una diferencia de unos 0,5 dB, justo el límite permitido.

Dado que no se cumple fielmente con las especificaciones requeridas y uno de los peores parámetros obtenidos es la adaptación a la entrada, se propone como mejora la introducción de una red de adaptación a la entrada. Al igual que se hizo en el Apartado III para el diseño del circuito de polarización, se introducirá un doble stub que maximice la adaptación del divisor. Tomando como ancho de los stubs el mismo que para una línea de impedancia  $50\,\Omega$ , se ajustarán los largos de ambos con la herramienta Tuner hasta encontrar las mejores condiciones.

| $L_{stub\_serie}$ (mm) | $L_{stub\_paralelo}$ (mm) |

|------------------------|---------------------------|

| 3.32                   | 4.94                      |

Cuadro 10: Longitudes de los stubs de la red de adaptación de entrada

Tras varios ajustes, se obtienen como mejores longitudes las indicadas en la Tabla 8. Gracias a esta red, se consigue que la adaptación a la entrada sea igual a  $-65,95\,\mathrm{dB}$ , un valor muy superior a los  $-20\,\mathrm{dB}$  requeridos. Además, no sólo de mejora esta condición, si no que a la salida se obtienen mejores aislamientos, como se puede apreciar en la Figura 37.

Figura 37: Aislamiento con red de adaptación a la entrada

Dado que la adaptación a la salida también ha mejorado, hasta el punto de que todos los puertos logran una adaptación superior a 15 dB, cabe esperar que la potencia de salida por los mismos se haya visto mejorada también. Observando la Figura 38, se puede apreciar una ligera mejora en la potencia de salida, incrementando en un valor de aproximadamente 0,2 dB, estando los puertos 2 y 4 muy próximos a entregar un tercio de la potencia recibida. La discrepancia entre puertos sigue siendo igual a 0,5 dB, el límite de lo especificado.

Figura 38: Potencia a la salida con red de adaptación a la entrada

Tras este añadido, el layout resultante del divisor de potencia es el mostrado en la figura siguiente:

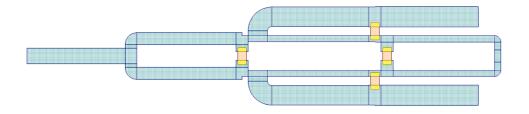

Figura 39: Layout del divisor de potencia con red de adaptación a la entrada

#### 4.3. Elemento radiante

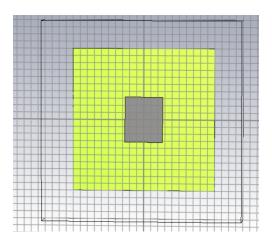

Para este apartado se va a hacer uso de CST Microwave Studio para el diseño y análisis de los elementos radiantes del circuito. Para el diseño de dichos elementos radiantes se utilizará:

$$f_0 = f_c + \Delta f[\text{GHz}] = 18,66 \text{ GHz}$$

(21)

Además, se ha elegido como sustrato para el diseño politetrafluoroetileno (teflón), el cuál ofrece los siguientes valores de permitividad dieléctrica y grosor:

$$\varepsilon_r = 2, 2 \tag{22}$$

$$H = 0.127 \,\mathrm{mm}$$

(23)

Con estos valores dados por el sustrato se obtienen los parámetros de diseño de la antena:

$$W = \frac{c}{2f} \sqrt{\frac{2}{\varepsilon_r + 1}} = 6,355 \,\text{mm} \tag{24}$$

$$L = \frac{c}{2f\sqrt{\varepsilon_r}} - 2\Delta L = 5{,}314\,\mathrm{mm} \tag{25}$$

Donde el valor de  $\Delta L$  viene dado de la siguiente manera:

$$\Delta L = 0.412H \frac{(\varepsilon_{\text{eff}} + 0.3) \left(\frac{W}{H} + 0.264\right)}{(\varepsilon_{\text{eff}} + 0.258) \left(\frac{W}{H} + 0.8\right)} = 0.05268 \,\text{mm}$$

(26)

$$\varepsilon_{\text{eff}} = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \frac{1}{\sqrt{1 + 12\frac{H}{W}}} = 2,1389 \tag{27}$$

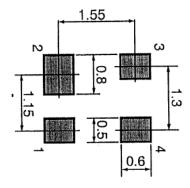

De esta manera, con W y con L se obtienen las dimensiones finales de nuestra antena parche, que quedará configurada de la siguiente manera:

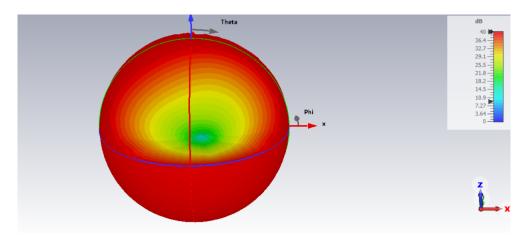

Figura 40: Diagrama de radiación de la antena parche

Ahora, una vez realizado el modelado de la geometría y del plano de masa (la geometría debe estar cerrada por condiciones de contorno para limitar el volumen donde el simulador tiene que calcular los campos electromagnéticos) se pasa a la simulación para observar los resultados.

#### 4.3.1. Antena de parche con plano de masa infinito

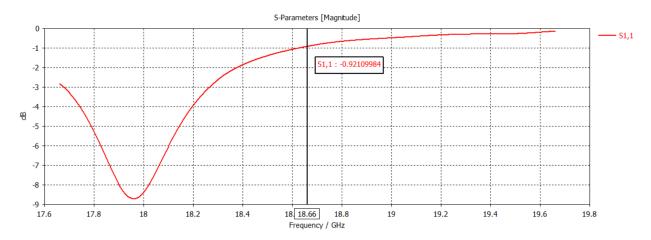

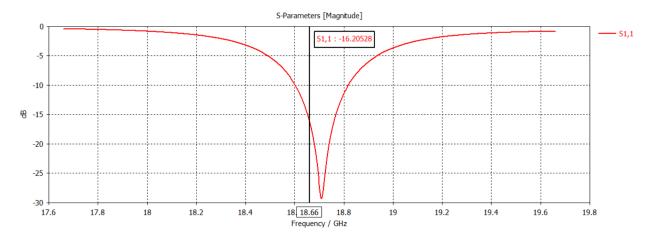

Una vez finalizado el proceso de simulación, se pueden observar los resultados de los distintos parámetros de nuestra antena. En primer lugar, los parámetros S:

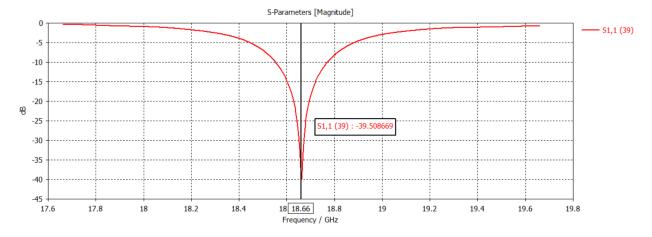

Figura 41: Parámetro  $S_{11}$  de la antena para los valores dados de W-L

En la Figura 41 se observa como a la frecuencia de trabajo (18,66 GHz), el valor del parámetro  $S_{11}$  es de -0.921 dB, lo que indica que la antena no está adaptada. Para conseguir la adaptación, se ha realizado un barrido por separado de los parámetros W y L con en fin de encontrar los valores óptimos para cada uno de ellos y el resultado ha sido el siguiente:

Figura 42: Parámetro  $S_{11}$  de la antena para los nuevos valores de W-L

Ahora sí, se puede observar cómo para nuestra frecuencia de 18,66 GHz la antena está adaptada, con un valor de  $S_{11}$  igual a -39,508 dB. Para conseguir este valor, tras el barrido se ha concluido que los valores óptimos son  $\mathbf{W} = \mathbf{9.5}$  mm y  $\mathbf{L} = \mathbf{5.0895}$  mm.

Con el valor de L se desplaza la frecuencia de adaptación en el eje de frecuencias hasta ajustarlo a la frecuencia de trabajo, y con el valor de W se mejora el valor de adaptación conseguida.

En la Figura 42 se mide el ancho de banda de la antena que garantiza un coeficiente de reflexión menor a 10 dB. Para ello, con dos marcadores, uno en cada punto de la gráfica con

valor  $-10 \,\mathrm{dB}$ , se observa la diferencia:  $18,756 - 18,540 \,\mathrm{[GHz]} = 216 \,\mathrm{MHz}$ .

A partir de los resultados de las simulaciones, se puede observar también cómo varía la potencia aceptada ( $P_{acc}$ ) y la potencia radiada ( $P_{rad}$ ) de la antena a medida que se consigue la adaptación:

Figura 43: Variación de la potencia aceptada en función de la adaptación de la antena

Como se puede ver, cuando no se disponía de la adaptación ( $S_{11} = -0.02 \,\mathrm{dB}$ ), el valor de la potencia aceptada era prácticamente nulo,  $P_{\mathrm{acc}} = 0.0023 \,\mathrm{W}$ , lo cuál tiene sentido. Una vez conseguida la adaptación, se obtiene para la frecuencia de trabajo un valor de  $P_{\mathrm{acc}} = 0.49993 \,\mathrm{W}$ .

En cuanto a la potencia radiada, sin adaptación se dispone de un valor de  $P_{\rm rad} = 0.00234$  W y con adaptación, de  $P_{\rm rad} = 0.494$  W. Esto es bastante lógico, ya que cuando se tiene adaptación, la potencia aceptada y la potencia radiada son prácticamente iguales.

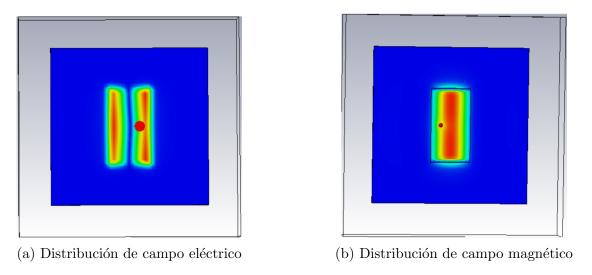

#### I. Distribuciones de campo eléctrico, campo magnético y corrientes superficiales

Una vez adaptada ya la antena, se pasa a la visualización de las distribuciones de campo. En la Figura 44 se observan las distribuciones de campo tanto eléctrico como magnético.

Figura 44: Distribuciones de campo de la antena parche

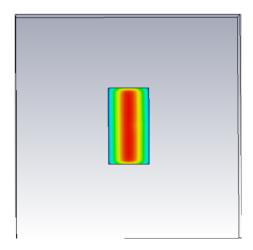

Para representar la intensidad de campo se oculta el sustrato para visualizarlo mejor y el resultado es el siguiente:

Figura 45: Intensidad de campo de la antena parche

Como se puede observar en CST, si se representan las distribuciones de campo con flechas, se aprecia que se trata de una antena parche con **polarización lineal**, siendo el campo E y el campo H ortogonales entre sí.

#### II. Diagramas de radiación

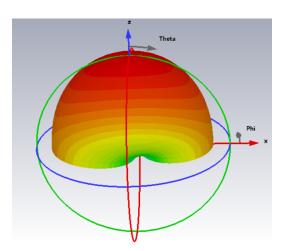

En cuanto al diagrama de radiación de la antena parche, se observa lo siguiente:

Figura 46: Diagrama de radiación de la antena parche

Este coincide con la forma del diagrama de una antena parche, y en este caso se obtiene un valor de directividad de  $D=8,185\,\mathrm{dBi}$ .

Sobre la ganancia, se obtiene cambiando las propiedades del diagrama de radiación, y en este caso brinda un valor de  $G=8,155\,\mathrm{dBi}$ , un poco inferior, pero prácticamente idéntico al valor de directividad.

En cuanto a los tipos de ganancia, se distingue la **ganancia real**, que es la ganancia que se obtiene teniendo en cuenta los factores de entorno y pérdidas del sistema. En este caso, el valor de la ganancia real es de 8.154 dBi, ya que los materiales utilizados son ideales y no tienen

pérdidas, por lo que prácticamente toda la potencia introducida será radiada.

A continuación, se estudia el axial ratio para corroborar el tipo de polarización que tiene la antena:

Figura 47: Axial Ratio de la antena parche

Se observa que el valor del  $AR=40~\mathrm{dB}$ , lo que muestra que efectivamente se trata de una polarización lineal. Para que se trate de una polarización circular debería salir un  $AR=0~\mathrm{dB}$ , lo que significaría que ambos semiejes son idénticos. Al tener un semieje tan grande comparado con el otro, como se aprecia en este caso (40 dB), se aproxima la polarización a una de tipo lineal.

#### 4.3.2. Antena de parche con plano de masa finito

A continuación se estudian los efectos de utilizar un plano de masa de tamaño finito. Para ello, se colocan los planos finitos en ambas caras del sustrato y se observa como varían los resultados con los obtenidos anteriormente.

En primer lugar se aprecia el parámetro  $S_{11}$  una vez introducidos dichos planos:

Figura 48: Parámetro  $S_{11}$  de la antena introduciendo planos de masa finitos

Como se deduce de la figura anterior, se produce una desadaptación a la frecuencia de trabajo, y el valor de  $S_{11}$  baja desde los -39.508 dB hasta los -16.205 dB.

En cuanto a la directividad de la antena teniendo en cuenta los nuevos planos de masa finitos:

| farfield (f=18.66) [1] |                   |  |  |  |

|------------------------|-------------------|--|--|--|

| Type                   | Farfield          |  |  |  |

| Approximation          | enabled (kR >> 1) |  |  |  |

| Component              | Abs               |  |  |  |

| Output                 | Directivity       |  |  |  |

| Frequency              | 18.66 GHz         |  |  |  |

| Rad. Effic.            | -0.05255 dB       |  |  |  |

| Tot. Effic.            | -0.1579 dB        |  |  |  |

| Dir.                   | 9.064 dBi         |  |  |  |

Figura 49: Valor de la directividad con planos de masa finitos

Al introducir los planos de masa finitos la directividad ha aumentado desde  $D=8,185\,\mathrm{dBi}$  hasta conseguir  $D=9,064\,\mathrm{dBi}$ . Además, al no haberse introducido las pérdidas todavía, se ve como el valor de la ganancia real sigue siendo similar al de la directividad, obteniéndose un valor de ganancia igual a  $8.906\,\mathrm{dBi}$

Para explicar estos resultados obtenidos se han realizado diversas simulaciones con distintos tamaños del sustrato. En primer lugar, al variar el tamaño del sustrato se aprecia que varía también la frecuencia de adaptación de la antena. Cuanto mayor es el tamaño del sustrato, más alta se torna la frecuencia a la que se consigue adaptar la antena.

Además, la directividad también varía conforme aumenta el tamaño del sustrato, por lo que se busca el tamaño para el cuál se consigue que nuestra directividad sea máxima.

Lo siguiente es introducir las pérdidas del material. Para ello, al sustrato se le introduce una tangente de pérdidas  $tan\delta = 0,009$ .

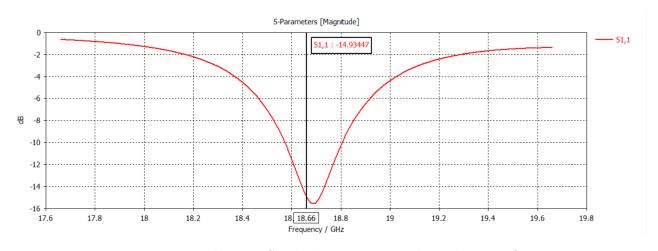

El parámetro  $S_{11}$  de la antena se ha visto modificado quedando de la siguiente manera:

Figura 50: Parámetro  $S_{11}$  de la antena con plano de masa finito

Como puede verse, la adaptación se ha reducido bastante en comparación con el caso anterior, pasando de -16.205 dB hasta los -14.93 dB actuales, cumpliendo así con la adaptación de

#### 14 dB requerida.

En el caso de la directividad y la ganancia, también se ven afectadas al utilizar esta nueva disposición:

| farfield (f=18.66) [1] |                   | farfield (f=18.66) [1] |                   |

|------------------------|-------------------|------------------------|-------------------|

| Type                   | Farfield          | Type                   | Farfield          |

| Approximation          | enabled (kR >> 1) | Approximation          | enabled (kR >> 1) |

| Component              | Abs               | Component              | Abs               |

| Output                 | Directivity       | Output                 | Realized Gain     |

| Frequency              | 18.66 GHz         | Frequency              | 18.66 GHz         |

| Rad. Effic.            | -1.872 dB         | Rad. Effic.            | -1.872 dB         |

| Tot. Effic.            | -2.014 dB         | Tot. Effic.            | -2.014 dB         |

| Dir.                   | 9.032 dBi         | Rizd. Gain             | 7.019 dBi         |

(a) Directividad de la antena

(b) Ganancia real de la antena

Figura 51: Información de los diagramas de radiación

Aquí se puede apreciar que los valores de directividad y ganancia ya no son iguales. En este caso, la directividad se queda en 9.032 dBi, mientras que la ganancia real disminuye hasta los 7.019 dBi debido a las pérdidas introducidas en el material.

Si se deseara que dichos valores se igualasen, es decir, si se quisiera mejorar la eficiencia de radiación de la antena, una buena opción sería mejorar el dieléctrico. Disminuyendo la tangente de pérdidas del dieléctrico se lograría reducir las pérdidas del sistema y aumentar así la ganancia real. Ya se ha comprobado que al introducir los planos de masa finitos la eficiencia de radiación se veía afectada en menor magnitud ( $D=9,064\,\mathrm{dBi}$  y  $G=8,906\,\mathrm{dBi}$ ), por lo que podría ser preferible mejorar el dieléctrico antes que el conductor.

#### 4.3.3. Array de antenas

En esta parte de la práctica, se realiza un análisis de la antena de parche diseñada en un array de dos elementos.

Para ello, en primer lugar se determina la distancia necesaria entre ellos para que no haya lóbulos secundarios. Por lo tanto, en base a la teoría, la distancia debe cumplir  $d < \lambda/2$ . En el caso límite se obtiene una distancia de:

$$d = \frac{\lambda}{2} = \frac{3 \cdot 10^8}{18,66 \cdot 10^9 \cdot 2} = 8,0385 \,\text{mm}$$

(28)

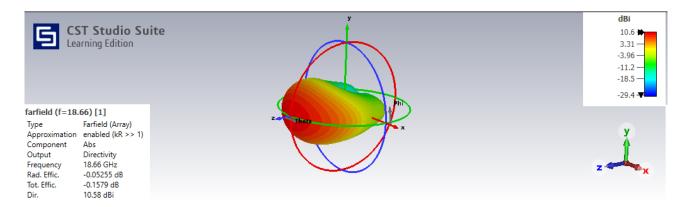

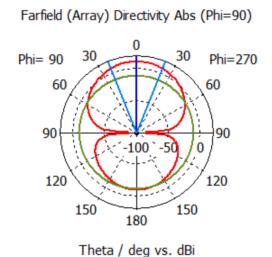

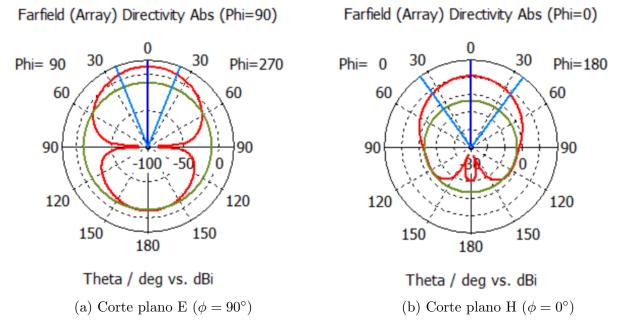

Con esta, se simula el array colocando dos elementos en el eje y y se obtienen los siguientes diagramas:

Figura 52: Diagrama 3D del array

Figura 53: Corte plano E $(\phi=90^\circ)$  del diagrama del array

Como se puede apreciar en la Figura 52, la directividad mejora hasta alcanzar un valor de  $D=10,58\,\mathrm{dBi}$ . Además, como se escoge el valor límite para la distancia entre elementos, en la Figura 53 no se observan lóbulos secundarios. En cuanto al ancho de haz, se mide en los cortes correspondientes al plano E ( $\phi=90^\circ$ ) y al plano H ( $\phi=0^\circ$ ) definidos de esta forma al haber colocado las antenas a lo largo del eje y.

Figura 54: Cortes del diagrama del array

Por lo tanto, los anchos de haz obtenidos para cada plano son  $\Delta\theta_E=43.6^{\circ}$  y  $\Delta\theta_H=72.9^{\circ}$ .

A partir de los valores anteriores, se obtiene la directividad aproximada según la teoría:

$$D = \frac{41253}{\Delta\theta_E \cdot \Delta\theta_H} = 12,979 \Rightarrow 11,13dBi \tag{29}$$

Se observa que el valor obtenido no es exactamente el mismo que el indicado por el programa. Esto se debe a que la expresión utilizada en (29) es una aproximación y a que CST realiza la simulación del factor de array a partir de un post-procesado de la radiación producida por un único elemento y los caminos recorridos a cada punto en el que se calcula el nuevo diagrama en función de la posición de cada elemento del array. Con ello, el objetivo es reducir el tiempo de simulación.

# 5. Integración

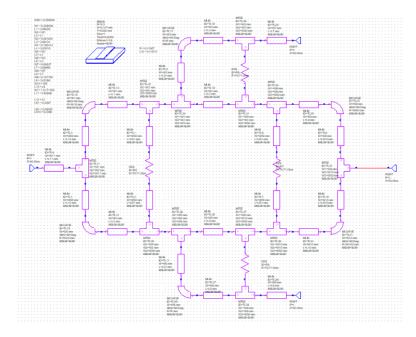

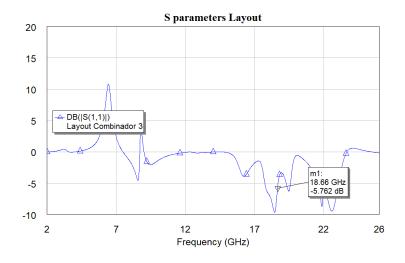

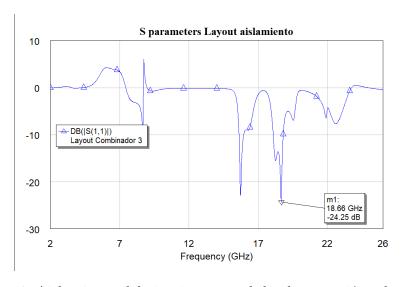

Una vez obtenidos los diseños de la red activa de alimentación y del elemento radiante, se estimará del funcionamiento del circuito total integrando ambas partes. Para ello, es necesario exportar el fichero del proyecto de CST en formato TOUCHSTONE e importarlo en un nuevo proyecto de AWR. Una vez importado, se deben cambiar los puertos de salida del subcircuito por los recién importados.

Con los puertos colocados en sus respectivas posiciones, se realiza una simualción para ver como cambian los resultados con los obtenidos en el Apartado 4.2. En este caso el aislamiento (parámetro  $S_{11}$ ) resulta de la siguiente manera:

Figura 55: Aislamiento del circuito en el puerto de entrada

Comparando con el resultado obtenido anteriormente, se observa que el aislamiento se ha deteriorado hasta los -5.762 dB. Para mejorar dicho aislamiento, se propone introducir una red de adaptación a la entrada del amplificador. Con dicha red introducida, en resultado del aislamiento es el siguiente:

Figura 56: Aislamiento del circuito con red de alimentación a la entrada

Además, se ve como en este caso, el circuito sólo está adaptado a la frecuencia de trabajo. Esto se debe a que los parámetros de las antenas han sido adaptados para dicha frecuencia, por lo que fuera de este valor, el aislamiento en el puerto de entrada baja notoriamente al producirse reflexión en cada uno de los puertos donde están situadas.

A parte del aislamiento, se observa como la fase del parámetro  $S_{11}$  también se ha visto afectada, pasando a tener un valor de -10° (equivalentes a los -1450° que se ven en la gráfica).

Figura 57: Desfase en el puerto de entrada al circuito

Este cambio de fase es debido también al funcionamiento de las antenas a la frecuencia de trabajo. El desfase producido por los puertos ideales de  $50\,\Omega$  es distinto al que producen estas antenas. Sólo importará la fase a ésta frecuencia, ya que en el resto de frecuencias el puerto de entrada no se encontrará aislado al producir las antenas altas reflexiones.

### 6. Conclusiones

Esta práctica tuvo como objetivo el diseño de un amplificador usado para un radar en el funcionamiento de la banda K. Se estudiaron por separado tanto la red activa como la parte radiante para luego realizar un análisis del circuito integrado.

En cuanto a la red de alimentación activa, se obtuvo un diseño óptimo en lo que respecta al circuito previo a la fabricación, cumpliendo con creces las especificaciones requeridas. Sin embargo, en su modelado a un circuito impreso, algunas de sus características empeoraron, como son la potencia de salida y el desequilibro entre puertos. Esto demuestra la dificultad de llevar a la práctica un diseño completo que cumpla con todas las condiciones necesarias.

La parte radiante del circuito se llevó a cabo también con bastante precisión, consiguiendo una directividad adecuada. Pese a esto, el resultado experimental no llega a coincidir exactamente con el resultado teórico, dado que la herramienta software utilizada no es capaz de simular con exactitud el factor de array.

Por último, la integración de ambas partes en un mismo circuito modifica algunas de las características del diseño individual. Se puede apreciar un peor aislamiento en la entrada y un cambio de fase en la misma. Es necesario volver a añadir una red de adaptación que mejore este problema.

Como trabajo futuro, se podría refinar el layout de la parte activa para cumplir con todas las especificaciones, así como mejor la integración de ambas partes y llevar a la realidad el diseño propuesto y probarlo experimentalmente.

# Índice de figuras

| 1.  | Esquema general de la practica                                             | . 2  |

|-----|----------------------------------------------------------------------------|------|

| 2.  | Circuito de polarización con circuito integrado                            | . 6  |

| 3.  | Circuito de polarización con elementos de aislamiento                      | . 6  |

| 4.  | Parámetros $S$                                                             | . 7  |

| 5.  | Figura de ruido                                                            | . 7  |

| 6.  | Factor de Rollet                                                           | . 8  |

| 7.  | Circunferencias de estabilidad                                             | . 9  |

| 8.  | Circunferencias de ruido                                                   | . 9  |

| 9.  | Ganancia disponible y circunferencias de ruido                             | . 10 |

| 10. | Circuito de polarización                                                   | . 11 |

| 11. | Parámetros S                                                               | . 12 |

| 12. | Circuito con adaptación a la entrada                                       | . 12 |

| 13. | Figura de ruido a la entrada con adaptación                                | . 13 |

| 14. | Circunferencias de ruido con adaptación a la entrada                       |      |

| 15. | Circuito con adaptación a la entrada y a la salida                         | . 14 |

| 16. | Valores finales de los parámetros de diseño                                | . 14 |

| 17. | Primer diseño posible de divisor de potencia                               | . 16 |

| 18. | Divisor Wilkinson                                                          | . 17 |

| 19. | Parámetros S para el primer diseño                                         | . 17 |

| 20. | Segundo diseño posible de divisor de potencia                              | . 18 |

| 21. | Parámetros S para el segundo diseño                                        |      |

| 22. | Tercer diseño posible de divisor de potencia                               | . 19 |

| 23. | Parámetros S para el tercer diseño                                         |      |

| 24. | Aislamiento y aislamiento cruzado para el tercer diseño                    |      |

| 25. | Cálculo del ancho y largo del stub en serie usando TXLine                  | . 22 |

| 26. | Uso de la herramienta <i>Tuner</i>                                         | . 22 |

| 27. | Parámetros S usando líneas microstrip                                      | . 23 |

| 28. | Ejemplo de implementación del encapsulado                                  | . 24 |

| 29. | Modelado del transistor sugerido por el fabricante                         | . 24 |

| 30. | Layouts                                                                    |      |

| 31. | Resultado final del circuito de polarización                               | . 25 |

| 32. | Layout del circuito de polarización                                        | . 25 |

| 33. | Circuito divisor de potencia con líneas reales y encapsulados              |      |

| 34. | Layout del divisor de potencia                                             | . 26 |

| 35. | Aislamiento                                                                | . 27 |

| 36. | Potencia a la salida                                                       | . 27 |

| 37. | Aislamiento con red de adaptación a la entrada                             | . 28 |

| 38. | Potencia a la salida con red de adaptación a la entrada                    |      |

| 39. | Layout del divisor de potencia con red de adaptación a la entrada          | . 29 |

| 40. | Diagrama de radiación de la antena parche                                  | . 30 |

| 41. | Parámetro $S_{11}$ de la antena para los valores dados de W-L $\ldots$     | . 31 |

| 42. | Parámetro $S_{11}$ de la antena para los nuevos valores de W-L             | . 31 |

| 43. | Variación de la potencia aceptada en función de la adaptación de la antena | . 32 |

| 44. | Distribuciones de campo de la antena parche                                | . 32 |

| 45. | Intensidad de campo de la antena parche                                    | . 33 |

| 46. | Diagrama de radiación de la antena parche                                  | . 33 |

| 47. | Axial Ratio de la antena parche                                                        | 34 |

|-----|----------------------------------------------------------------------------------------|----|

| 48. | Parámetro $S_{11}$ de la antena introduciendo planos de masa finitos                   | 34 |

| 49. | Valor de la directividad con planos de masa finitos                                    | 35 |

| 50. | Parámetro $S_{11}$ de la antena con plano de masa finito $\ldots \ldots \ldots \ldots$ | 35 |

| 51. | Información de los diagramas de radiación                                              | 36 |

| 52. | Diagrama 3D del array                                                                  | 37 |

| 53. | Corte plano E ( $\phi = 90^{\circ}$ ) del diagrama del array                           | 37 |

| 54. | Cortes del diagrama del array                                                          | 38 |

| 55. | Aislamiento del circuito en el puerto de entrada                                       | 39 |

| 56. | Aislamiento del circuito con red de alimentación a la entrada                          | 39 |

| 57. | Desfase en el puerto de entrada al circuito                                            | 40 |

# Índice de cuadros

| 1.  | Amplificador de bajo ruido                                                      | 3  |

|-----|---------------------------------------------------------------------------------|----|

| 2.  | Divisor de potencia                                                             | 3  |

| 3.  | Elemento radiante                                                               | 3  |

| 4.  | Valores de impedancias y resistencias (en $\Omega$ ) del primer diseño          | 17 |

| 5.  | Valores de impedancias y resistencias (en $\Omega$ ) del segundo diseño         | 18 |

| 6.  | Valores de impedancias y resistencias (en $\Omega$ ) del tercer diseño $\ldots$ | 20 |

| 7.  | Propiedades de Sustratos                                                        | 21 |

| 8.  | Valores de L (mm) para las líneas reales de la red de adaptación                | 22 |

| 9.  | Valores de W_mlin y L_mlin para las líneas                                      | 23 |

| 10. | Longitudes de los <i>stubs</i> de la red de adaptación de entrada               | 28 |